Printed Circuit Board Design Guidelines

Printed Circuit Board Design Guidelines

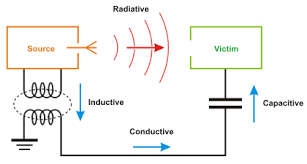

Below is a list of 16 EMC design guidelines for printed circuit boards along

with a short justification for each.

1. The lengths of traces

carrying high-speed digital signals or clocks should be minimized.

High-speed digital signals and clocks are

often the strongest noise sources. The longer these traces are, the more

opportunities there will be to couple energy away from these traces. Remember

also, that loop area is generally more important than trace length. Make sure

that there is a good high-frequency current return path very near each trace.

2. The lengths of traces

attached directly to connectors (I/O traces) should be minimized.

Traces attached directly to connectors are

likely paths for energy to be coupled on or off the board.

3. Signals with

high-frequency content should not be routed beneath components used for board

I/O.

Traces routed under a component can

capacitively or inductively couple energy to that component.

4. All connectors should

be located on one edge or on one corner of a board.

Connectors represent the most efficient

antenna parts in most designs. Locating them on the same edge of the board

makes it much easier to control the common-mode voltage that may drive one

connector relative to another.

5. No high-speed

circuitry should be located between I/O connectors.

Even if two connectors are on the same edge of

the board, high-speed circuitry located between them can induce enough

common-mode voltage to drive one connector relative to the other resulting in significant

radiated emissions.

6. Critical signal or

clock traces should be buried between power/ground planes.

Routing a trace on a layer between two solid

planes does an excellent job of containing the fields from these traces and

prevents unwanted coupling.

7. Select active digital

components that have maximum acceptable off-chip transition times.

If the transition times of a digital waveform

are faster than they need to be, the power in the upper harmonics can be much

higher than necessary. If the transitions times of the logic employed are

faster than they need to be, they can usually be slowed using series resistors

or ferrites.

8. All off-board

communication from a single device should be routed through the same connector.

Many components (especially large VLSI

devices) generate a significant amount of common-mode noise between different

I/O pins. If one of these devices is connected to more than one connector, this

common-mode noise will potentially drive a good antenna. (The device will also

be more susceptible to radiated noise brought in on this antenna. )

9. High-speed (or

susceptible) traces should be routed at least 2X from the board edge, where X

is the distance between the trace and its return current path.

The electric and magnetic field lines

associated with traces very near the edge of a board are less well contained.

Crosstalk and coupling to and from antennas tends to be greater from these

traces.

10. Differential signal trace pairs should be

routed together and maintain the same distance from any solid planes.

Differential signals are less susceptible to

noise and less likely to generate radiated emissions if they are balanced (i.e.

they have the same length and maintain the same impedance relative to other

conductors).

11. All power (e.g.

voltage) planes that are referenced to the same power return (e.g. ground)

plane, should be routed on the same layer.

If, for example, a board employs three

voltages 3.3 volts, 3.3 volts analog and 1.0 volt; then it is generally

desirable to minimize the high-frequency coupling between these planes. Putting

the voltage planes on the same layer will ensure that there is no overlap. It

will also help to promote an efficient layout, since the active devices are

unlikely to require two different voltages at any one position on the board.

12. The separation

between any two power planes on a given layer should be at least 3 mm.

If two planes get too close to each other on

the same layer, significant high-frequency coupling may occur. Under adverse

conditions, arcing or shorts may also be a problem if the planes are too

closely spaced.

13. On a board with power

and ground planes, no traces should be used to connect to power or ground.

Connections should be made using a via adjacent to the power or ground pad of

the component.

Traces on a connection to a plane located on a

different layer take up space and add inductance to the connection. If

high-frequency impedance is an issue (as it is with power bus decoupling

connections), this inductance can significantly degrade the performance of the

connection.

14. If the design has

more than one ground plane layer, then any connection to ground at a given

position should be made to all of the ground layers at that position.

The overall guiding principle here is that

high-frequency currents will take the most beneficial (lowest inductance) path

if allowed to. Don't try to direct the flow of these currents by only

connecting to specific planes.

15. There should be no

gaps or slots in the ground plane.

It's usually best to have a solid ground

(signal return) plane and a layer devoted to this plane. Any additional power

or signal current returns that must be DC isolated from the ground plane should

be routed on layers other than the layer devoted to the ground plane.

16. All power or ground

conductors on the board that make contact with (or couple to) the chassis,

cables or other good "antenna parts" should be bonded together at

high frequencies.

Unanticipated voltages between different

conductors both nominally called "ground" are a primary source of

radiated emission and susceptibility problems.

In addition to the 16 guidelines above, board

designers often employ guidelines that are specific to their industry. For

example, "Clock generation circuits employing phase-locked loops should

have their own isolated power derived from the board's power through a #1234

ferrite bead. " These guidelines based on experience can be invaluable to

the knowledgeable board designer. However, these same guidelines applied to

other designs with no concept of where they came from or why they work can

result is wasted effort and non-functional boards. It is very important to

understand the basic physics behind each and every guideline being applied.

It is also important to identify the potential

noise sources, antennas and coupling paths with every single design you

evaluate. The best design won't be the one that complies with the most

guidelines. The best design is the one that meets all of the specifications

with the lowest cost and highest reliability.

Thanks,

Ruby

Comments

Post a Comment